### 1 General Description

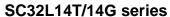

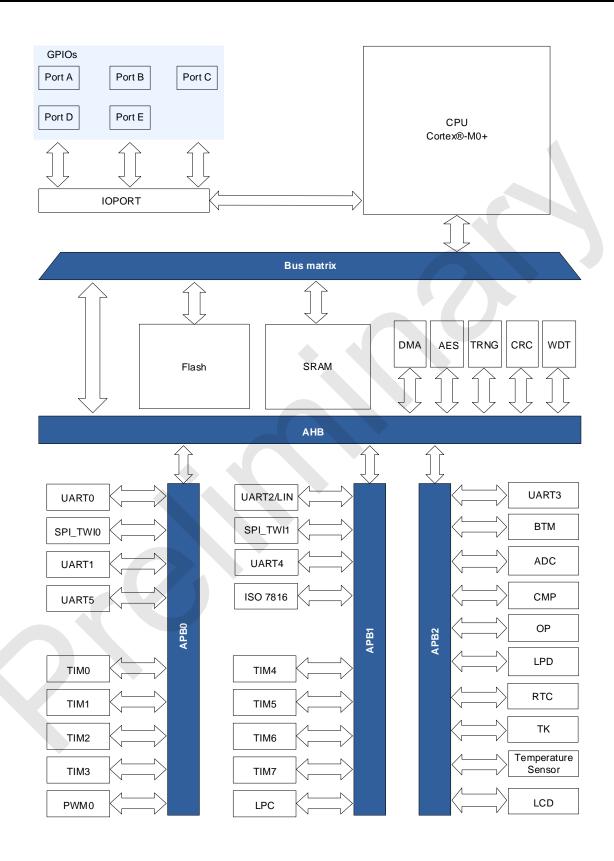

The SC32L14T/14G is an industrial-grade, ultra-low-power Flash microcontrollers based on the Arm Cortex<sup>®</sup>-M0+ core, featuring high-performance, low-power, and high-reliability applications. These microcontrollers operate at a high frequency of up to 48MHz. The Cortex<sup>®</sup>-M0+ core utilizes a 32-bit reduced instruction set architecture (RISC) and complies with the CMSIS standard. The SC32L14T/14G series offers powerful data processing capabilities, with an integrated Direct Memory Access (DMA) controller for high-speed data transfer. The hardware CRC module and the built-in 32-bit hardware multiplier further enhance the data computation speed. The embedded AES/TRNG function ensures comprehensive system security.

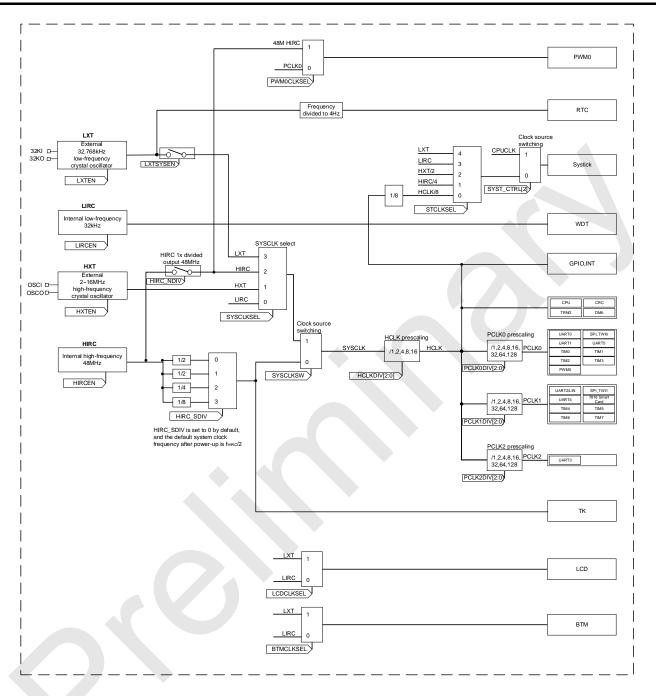

The SC32L14T/14G microcontrollers incorporate two clock sources: a high-precision high-frequency 48MHz oscillator (HIRC), a low-frequency 32kHz oscillator (LIRC). Additionally, they provide two external crystal oscillator interfaces: a 2-16MHz high-frequency crystal (HXT) interface and a 32.768 kHz low-frequency crystal (LXT) interface. The embedded clock sources and external crystal oscillator interfaces can supply the system clock, and the built-in system clock monitor module switches to HIRC as the clock source in case of system clock abnormalities, ensuring stable system operation.

The SC32L14T/14G series offers a wide range of peripheral resources: up to 77 GPIO pins, all pins maintain port status in sleep mode, support external interrupts, and wake-up the CPU in sleep mode; in addition, the series also has eight 16-bit timers, 1 low-power counter (LPC), 1 low-power basic timer (BTM), 8 channels of 16-bit multifunctional PWM with fault detection function; It also features 6 independent UARTs, among which UART2 features a complete LIN interface and support low-power wake-up; One 7816 SMCI; 2 multifunction communication ports (SPIO/1 & TWIO/1); built-in RTC perpetual calendar; support resistor and capacitor LCD driver mode; 32-channel high-sensitivity capacitive touch circuits; 1 analog comparator, 1 rail-to-rail OP, and 23 channels of 14-bit high-precision ADC. The microcontrollers come with an independent watchdog timer (WDT) and a highly reliable, configurable low-voltage reset circuit (LVR) to enhance system reliability. They provide three power modes to provide strong support for low-power design.

The SC32L14T/14G series delivers high performance and reliability, supporting operating voltage range of 1.8-5.5V and capable of operating stably in an ambient temperature range of -40°C to 105°C. They also exhibit excellent ESD performance and EFT immunity. In terms of process technology, the SC32L14T/14G series adopts the industry-leading eFlash process, allowing for more than 100,000 erase/write cycles and data retention of 100 years at room temperature. Regarding storage resources, the SC32L14T/14G series offers a maximum of 256 Kbytes of ROM space and 16 Kbytes of SRAM The SRAM also supports parity check functionality for enhanced system stability. Additionally, there is a 2 Kbytes user storage area (generic EEPROM), and a 4 Kbytes system storage area (LDROM). It includes a built-in system storage area to support OTA upgrades and provides multiple programming methods such as ISP (In-System Programming), ICP (In-Circuit Programming), and IAP (In-Application Programming), enabling on-board debugging and firmware updates while the chip is online or powered. This series utilizes the Cortex-M0+ core and is compatible with proven Keil & IAR debugging and development software, supporting both C and assembly language instructions.

The SC32L14T/14G series, with its exceptional low power consumption, constructs a secure environment through hardware-based AES combined with the TRNG, along with excellent anti-interference capabilities. It meets diversified requirements for secure encryption, low-power operation, high-reliability touch control, and main control integration. Its applications are extensive, covering the following fields: consumer electronics (such as interactive panels with touch/LCD for smart appliances, PC peripherals, gaming consoles, GPS devices), smart homes and IoT (such as smart controllers/thermostats, smart locks, wired/wireless sensors, remote gas/water meters), secure portable devices (such as payment terminals, medical handheld instruments, health and fitness devices, visual docking machines), and industrial control (such as industrial sensors, remote control, instruments with touch functionality, and HMI devices), among many others.

With its core advantages of security, reliability, precise interaction, and multi-scenario penetration, the SC32L14T/14G series provides a one-stop solution for high-performance, low-power MCUs, helping customers achieve intelligent, low-power, and highly reliable product design goals.

hardware co-processor for high-performance computation

### **Features**

### **Operating Conditions**

Operating voltage: 1.8V~5.5V

Operating temperature: -40 ~ +105℃

#### **EMS**

**ESD**

HBM: ANSI/ ESDA/JEDEC JS-001-2023 Class 3A

CDM: ANSI/ESDA/JEDEC JS-002-2022 Class C3

EN61000-4-4 Level 4

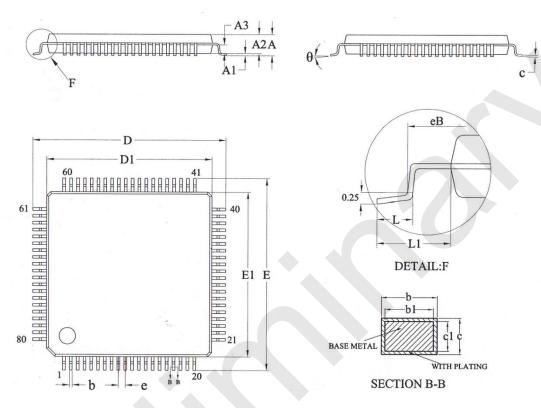

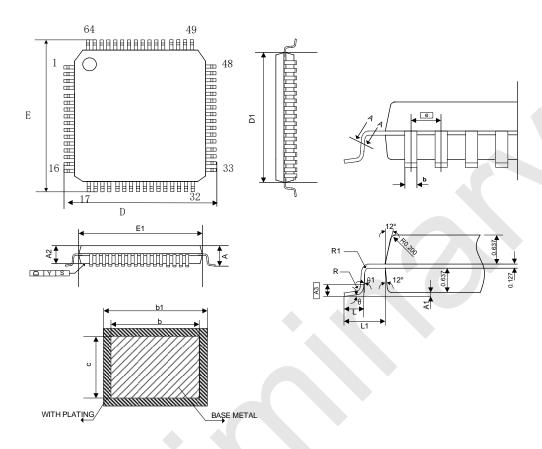

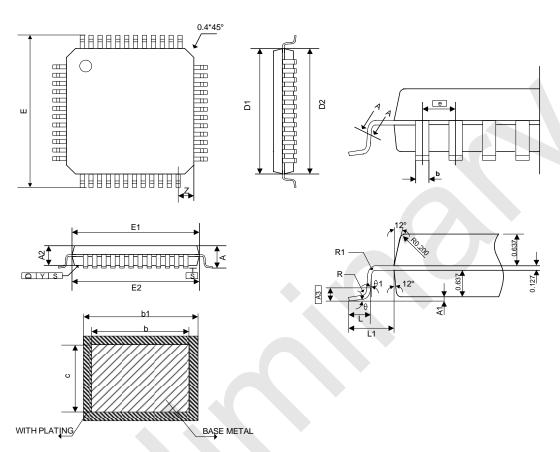

### **Package**

80 PIN: LQFP80 (12X12)

64 PIN: LQFP64 (10X10)

48 PIN: LQFP48 (7X7)/ QFN48 (5X5)

#### Core

- Cortex®-M0+ core

- With Wakeup Interrupt Controller (WIC) module

- With MPU module

- 64-bits instruction prefetch

- Built-in Multiplier Unit (MDU)

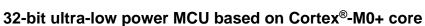

#### Reset

- Power-On Reset (POR)

- Software Reset

- Reset through external NRST pin (PE5) with a low-level signal

- Watchdog Timer (WDT) reset

- Low Voltage Reset (LVR)

- Four selectable reset voltages: 4.3V, 3.7V, 2.9V, 1.7V

- The default value is determined by the user's programmed Code Option

#### BUS

- 1 IOPORT

- 1 AHB

- 3 APB: APB0~APB2

#### **Low Power Consumption**

- Operation Mode: Typical operating power consumption is 150µA/MHz.

- IDLE Mode, can be woken up by any interrupt

- STOP Mode:

- Can be woken up by INT0~15, Base Timer, TK, UART0~5, RTC, LPC and CMP

- The typical base current in STOP Mode is as low as  $1\mu A@V_{DD}=5V$

- When the RTC is started in STOP Mode, the typical total current of the chip (including the LXT circuit current) is as low as 1.5μA@ V<sub>DD</sub>=5V

- When LCD display drive (no load) is enabled in STOP Mode, the typical total current of the chip is as low as 1.5µA @ V<sub>DD</sub>=5V

- Wake-up time in STOP Mode is no more than 36µs

#### **Advanced Encryption Standard (AES)**

- Support key length: 128/192/256-bit

- Supports chaining modes: ECB, CBC and CTR mode

- Supports working modes: encryption/decryption

- hardware-accelerated sampling architecture, with a dedicated

### True Random Number Generator (TRNG)

- Can generate 32-bit true random numbers

- If randomness is low, a seed error interrupt can be triggered

- Provide an interrupt when the random number generation is

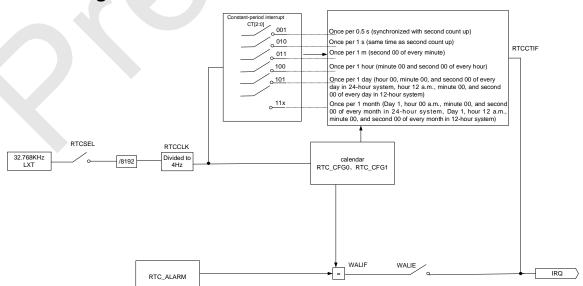

### Real-Time Clock (RTC)

- Clock source is LXT

- Can operate in low-power mode and supports wake-up from STOP Mode

- Calendar function

- Supports BCD format time/date registers

- Hardware automatically handles leap year corrections Accuracy follows the external 32.768K LXT

- Interrupt System

- Can set an alarm interrupt

- Can configure fixed interrupt periods: year, month, day, hour, minute, second, or half-second (0.5 seconds)

- Supports wake-up from STOP mode via interrupt events

- Time mode configuration

- Supports 24-hour or 12-hour time display modes

- Secure read/write mechanism

- Provides a half-second flag to avoid timing conflicts caused by the carry process

#### 2.1 Flash

### **APROM**

- Up to 256 Kbytes APROM

- Can be rewritten up to 100,000 times

- data retention of 100 years at room temperature

- Supports hardware read protection encryption

- Supports hardware write protection: Provides two regions for disabling IAP (In-Application Programming) operations. Users can configure the settings through the Code Option, with the minimum setting unit being 512 bytes (one sector)

#### **LDROM**

4 Kbytes of system storage area, factory-programmed with BootLoader program

#### SRAM

- 16 Kbytes Internal SRAM

- Supports parity check:

- An additional 2K RAM is used for parity checking, which means SRAM data bus width is 36 bits, with 4 bits dedicated to parity check (one bit per byte)

- The parity check bits are calculated and saved when writing to the SRAM, and automatically verified upon reading. If a bit fails, an unmaskable interrupt (Cortex®-M0+ NMI) will be generated

- Provides an independent SRAM parity error flag, SRAMPEIF

- Supports booting from SRAM

#### 2K Bytes User Storage Area (generic EEPROM)

- Divided into four 512 bytes sectors

- Can be rewritten up to 100,000 times

- Data retention time is over 100 years at room temperature

### 96 bits unique ID

96-bit Unique ID defined in the design option area

### **BootLoader**

- Hardware method: System storage area of 4 Kbytes, factoryprogrammed with BootLoader program

- Software method: Supports interrupt vector table remapping, allowing flexible partitioning of the APROM area for user BootLoader program execution

#### 2.3 Flash **Programming** and **Emulation**

- Programming methods supported: ICP / ISP / IAP

- 2-wire JTAG / SWD programming and emulation interface

- Simulation functionality is not supported in encrypted mode

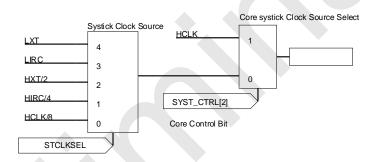

#### 2.4 Clock source

### Built-in high-frequency 48 MHz oscillator (HIRC)

- Can be selected as the system clock source

- The default clock frequency when power on "f<sub>SYS</sub>" is f<sub>HIRC</sub>/2

- Frequency Error: Within ±1% @ -40 ~ 105℃ @ 1.8V~ 5.5V

- The system clock can be automatically calibrated by 32.768 kHz external crystal oscillator, after calibration HIRC accuracy can be infinitely close to the accuracy of external 32.768 kHz crystal oscillator

### Built-in low-frequency 32 kHz oscillator (LIRC)

- Can be selected as the system clock source

- Fixed as the WDT clock source, which will be automatically enabled when WDT is enabled

- Can be selected as the Base Timer clock source and wake-up from STOP Mode

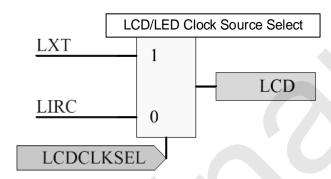

- Can be selected as the LCD clock source

- Frequency Error: Within ±4% @ 25°C @ 1.8V~ 5.5V

#### External 2~16MHz crystal oscillator (HXT)

- Can be selected as the system clock source

- User can choose an external crystal oscillator oscillating frequency of <12MHz or ≥12MHz

### External 32.768 kHz crystal oscillator (LXT)

- Can be selected as the system clock source

- Can be selected as the Base Timer clock source

- Can be selected as the LCD/LED clock source

- Allows for an external 32,768kHz oscillator

- Automatic calibration of HIRC can be performed using LXT

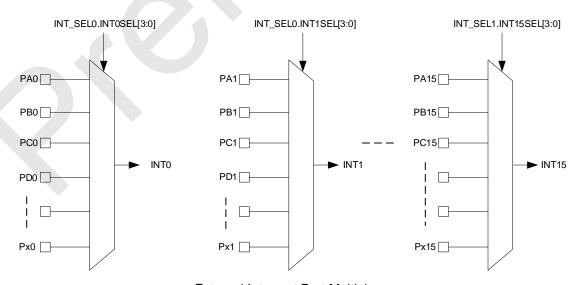

#### 2.5 Interrupts (INT)

- Up to 27 interrupts

- Four-level interrupt priority can be set External interrupts (INT):

- - 16 interrupts, occupying 4 interrupt vectors in total

- Change Interrupts on All GPIO pins

- All interrupts can be set as rising edge, falling edge, or both-edge interrupts, each with an independent corresponding interrupt flag

- Setting the corresponding interrupt flag in software triggers entry into the corresponding interrupt

#### 2.6 **Digital peripherals**

#### Up to 77 GPIOs

Independent pull-up resistor configuration is available

- IO sink current drive capability: 50mA@ V<sub>PIN</sub>=0.8V

- IO source current drive capability: 12mA@ V<sub>PIN</sub>=4.3V

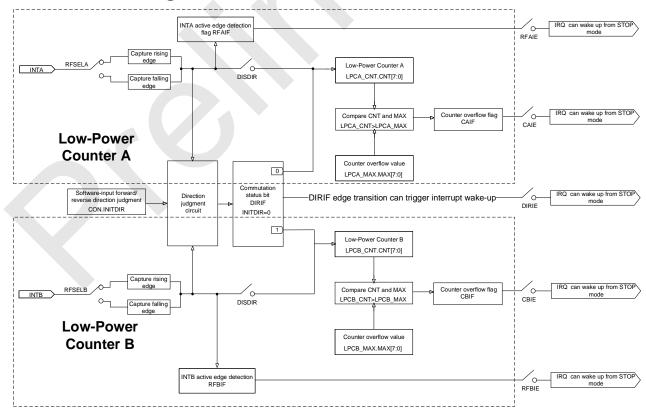

### A Two-Channel Input Low-Power Counter (LP Counter)

- Can be connected to devices such as linear or incremental encoders to obtain count, direction, and other information

- Counting in STOP mode to reduce MCU wake-up frequency and overall power consumption

- Provides two external signal input ports, INTA and INTB, which can independently detect the rising and falling edges of the input signals and count independently

- Edge detection can trigger an interrupt

- Count overflow can trigger an interrupt

- Direction information of the input signal can be determined by hardware

- Direction jump can trigger an interrupt

- LPC interrupt can wake up from STOP mode

### Watchdog timer (WDT)

Built-in WDT with programmable overflow time ranging from 3.94ms to 500ms

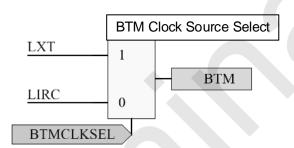

#### Base Timer (BTM)

- The clock sources LXT and LIRC are selectable

- Selectable interrupt frequency intervals from 15.625ms to 32s

- Can wake up from STOP Mode

#### 8 16-bit timers: Timer0~Timer7

- 16-bit up, down, and up/down auto-reload counters

- Supports rising edge/falling edge capture for PWM duty and

- Each TIM can provide two channels of synchronized and adjustable duty cycle PWM outputs (TPWMA/TPWMB).

- TIM1/2/6 timer overflow and capture events can trigger DMA

- Each Tn of TIM0~7 can be mapped to another sets of IO pins

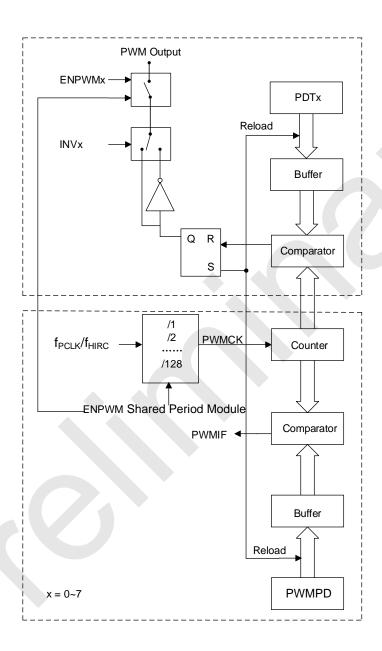

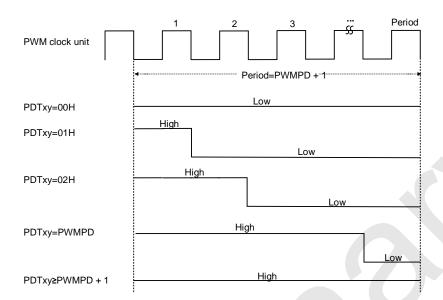

### 8 channels 16-bit Advanced PWM0

- The clock sources HIRC and PCLK are selectable

- Shared period and independently adjustable duty cycle

- Support dead time and complementary PWM output

- Support center-aligned mode

- Support fault detection (FTL)

#### 6 independent UART: UART0~5

- Independent baud rate generator

- UART0~5 all support wakeup from STOP Mode

- UART0~5 ports can be mapped to 2 sets of IO pins

- UART3 supports only half-duplex communication when mapped to programming / debugging port

- Three communication modes are optional:

- Mode 0, 8-bit half-duplex synchronous communication

- Mode 1, 10-bit full-duplex asynchronous communication

- Mode 2, reserved

- Mode 3, 11-bit full-duplex asynchronous communication

- UART2 has a full LIN interface, offering the following capabilities:

- Master and slave mode switching

- Hardware break transmission in master mode(10/13bits)

- Hardware break detection in slave mode(10/11bits)

- Baud rate synchronization in slave mode

- UART0 and UART1 support DMA requests

- UART2~5 do not support DMA requests

### 7816 Smart Card Interface (SMCI)

- The protocol complies with the ISO-7816-3 T=0 asynchronous half-duplex transmission protocol standard

- Supports Direct/Inverse Convention

- Programmable clock source frequency f<sub>SC</sub>

- Flexible and adjustable basic time unit (ETU)

- Configurable Extra Guard Time

- Data frame control:

- Supports programmable parity mode: even parity or no parity

- Automatically generate and detect parity bits

- Configurable stop bit length (1~2 bits)

- Error indication signal pulse width can be set

- Supports signal port mapping

#### 2 Advanced two in one Interface SPI0/1 & TWI0/1

- SPI0/1:

- Supports 8-bit or 16-bit communication mode

- Signal ports can be mapped to 3 additional set of ports Supports DMA

- TWI0/1:

- Supports master mode or slave mode

- Supports clock stretching in slave mode

- Communication speed up to 1Mbps

- Signal ports can be mapped to 3additional set of ports

- Supports DMA

#### **CRC**

- Initial value can be set, with a default of 0xFFFF\_FFF

- Polynomial can be programmed, with a default of 0x04C1\_1DB7

- Supports 8/16/32-bit data units

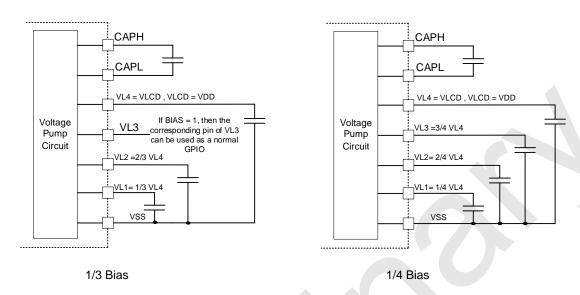

#### **LCD Driver**

- The clock sources LXT and LIRC are selectable

- Support display in STOP mode

- Support resistor and capacitor bias voltage generating circuit

- Resistor LCD driver supports fast charge mode, LCD voltage output port voltage divider resistor options: 11ΚΩ, 100ΚΩ, 300ΚΩ, 800ΚΩ

- Capacitive LCD driver is in capacitive bias mode. In this mode, the total power consumption of the LCD circuit can be as low as: 2~3µA @STOP mode

- LCD:

- Supports 8 X 51, 6 X 53, 5 X 54, or 4 X 55 segment LCD driving

- Two bias voltages options: 1/3 and 1/4

- Two waveform modes: Type A and Type B

- Three frame frequencies available:

- ◆ 32/64/128 Hz in Type A mode

- ♦ 64/128/256 Hz in Type B mode

#### **DMA**

- 2 independent configurable channels

- Each DMA channel can send DMA requests to other channels

- Data width supports byte, half-word, and word

- 20 DMA request sources with two priority levels

- Supports source/destination address auto-increment or fixed

- Supports single and burst transfer modes

- Transfer modes: memory to memory, memory to peripheral, peripheral to memory, peripheral to peripheral

## 2.7 Analog peripherals

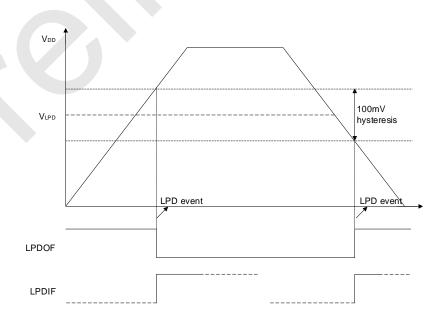

#### Low Voltage Detector (LPD):

- 8-level low-voltage detection:

- 1.85V / 2.05V / 2.25V / 2.45V / 2.65V / 2.85V / 3.05V /

3.25V

- Can generate interrupts

- The power supply of LPD is turned off in STOP mode

### 32-channel high-sensitivity Touch Key circuit

- Only supported by SC32L14T series

- Channels can be scanned in parallel

- 103 Capacitor must be connected between the CMOD pin and ground

- Has strong anti-interference ability and can pass 10V dynamic CS test

- Supports self-capacitance mode and mutual-capacitance mode

- Supports low-power mode

- Supports fast wake-up STOP mode

- Suitable for touch applications with high sensitivity requirements, such as proximity sensing and touch keys

- Comprehensive development support: Highly flexible touch software library, intelligent debugging software

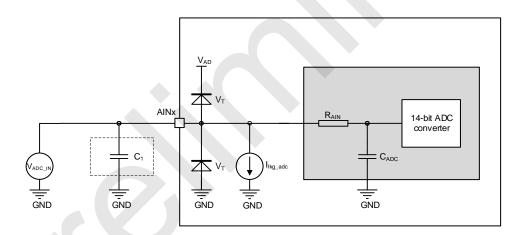

### **Analog-to-Digital Converter ADC**

- Precision: 14 bits

- Supports up to 23 channels

- External 20 ADC sampling channels can be multiplexed with I/O ports for other functions

- One internal ADC can directly measure V<sub>DD</sub> voltage

- One internal ADC can directly measure OP output

- One internal temperature sampling channel

- Four options for ADC reference voltage: V<sub>DD</sub>, and internal 2.048V, 1.024V, or 2.4V

- Configurable ADC conversion completion interrupt

- Supports single-channel continuous conversion mode

- Supports DMA transmission: DMA request will be generated after ADC conversion complete

- The conversion results feature an overflow flag: OVERRUN, and the OVERRUN flag bit is in the same register as the ADC conversion results so users can read the information all at once

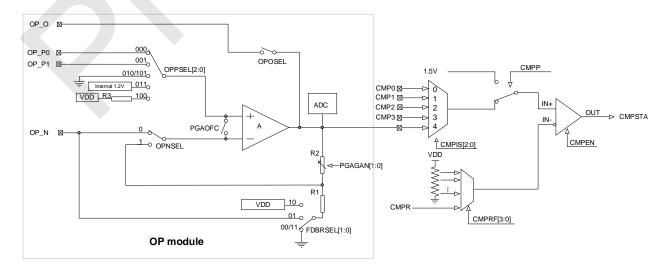

### **Operational Amplifier (OP)**

- A rail-to-rail input stage

- Can be configurable as a Programmable Gain Amplifier (PGA)

- Non-inverting gain: 8/16/32/64

- Inverting gain: 7/15/31/63

- Inverting gain: 7/15/31/63

Two external pins for the non-inverting input: OP\_P0 or OP\_P1

- One external pin for the inverting input: OP\_N

- One external pin for the output: OP\_O

- The output can be directly connected to the ADC input

- The output can be directly connected to the positive input of a Comparator (CMP)

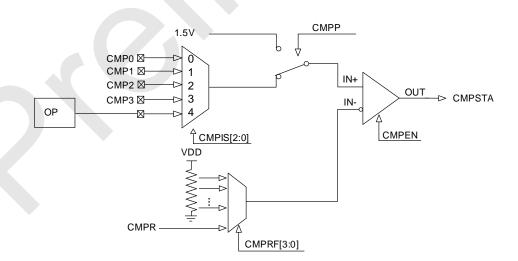

### **Analog Comparator CMP**

- Five positive input signals selectable:

- Four analog signal positive input terminals CMP0~CMP3

- OP output signal

- Negative input voltage can be selected from CMPR input or one of the 15 comparison voltages derived from the internal V<sub>DD</sub> voltage division

- CMP interrupts can wake up the STOP mode

#### **Temperature Sensor**

- The voltage value of temperature sensor can be measured by ADC

- Use internal 2.4V as reference voltage

- The conversion value of ADC will increase by a fixed value for every increase of 1°C

# **Product Peripheral Resource Table**

| Model Peripherals  |                              |                              | SC321<br>SC321               |                              |                              |                              |

|--------------------|------------------------------|------------------------------|------------------------------|------------------------------|------------------------------|------------------------------|

| Model Felipherals  | _M8                          | _R8                          | _C8                          | _M7                          | _R7                          | _C7                          |

| GPIOs              | 77                           | 61                           | 45                           | 77                           | 61                           | 45                           |

| APROM (Kbyte)      |                              | 256                          |                              |                              | 128                          |                              |

| SRAM (Kbyte)       |                              |                              | 1                            | 6                            |                              |                              |

| TK                 |                              | SC32L14                      | Γ_(with TK) &                | SC32L14G_(w                  | vithout TK)                  |                              |

| SPI                | 2                            | 2                            | 2                            | 2                            | 2                            | 2                            |

| TWI                | 2                            | 2                            | 2                            | 2                            | 2                            | 2                            |

| UART               | 6                            | 5                            | 2                            | 6                            | 5                            | 2                            |

| 7816 SMCI          | 1                            | 1                            | 0                            | 1                            | 1                            | 0                            |

| TIM                | 8                            | 8                            | 7                            | 8                            | 8                            | 7                            |

| LPC                | 1                            | 1                            | 1                            | 1                            | 1                            | 1                            |

| RTC                | 1                            | 1                            | 1                            | 1                            | 1                            | 1                            |

| PWM0               | 8                            | 8                            | 8                            | 8                            | 8                            | 8                            |

| AES                | 1                            | 1                            | 1                            | 1                            | 1                            | 1                            |

| TRNG               | 1                            | 1                            | 1                            | 1                            | 1                            | 1                            |

| OP                 | 1                            | 1                            | \                            | 1                            | 1                            | \                            |

| СМР                | 1                            | 1                            | \                            | 1                            | 1                            | \                            |

| ADC Channels       | 23                           | 18                           | 16                           | 23                           | 18                           | 16                           |

| LCD<br>COM X SEG   | 8X51<br>6X53<br>5X54<br>4X55 | 8X36<br>6X38<br>5X39<br>4X40 | 8X24<br>6X26<br>5X27<br>4X28 | 8X51<br>6X53<br>5X54<br>4X55 | 8X36<br>6X38<br>5X39<br>4X40 | 8X24<br>6X26<br>5X27<br>4X28 |

| CRC                |                              |                              | YE                           | S                            |                              |                              |

| DMA                |                              |                              | YE                           | ES                           |                              |                              |

| LPD                |                              |                              | YE                           | ES                           |                              |                              |

| Temperature Sensor |                              |                              | YE                           | S                            |                              |                              |

| Max. CPU frequency |                              |                              | 481                          | ИHz                          |                              |                              |

# **Ordering Information**

| PRODUCT ID    | PACKAGE | PACK |

|---------------|---------|------|

| SC32L14TM8PJR | LQFP80  | TRAY |

| SC32L14TM7PJR | LQFP80  | TRAY |

| SC32L14GM8PJR | LQFP80  | TRAY |

| SC32L14GM7PJR | LQFP80  | TRAY |

| SC32L14TR8PJR | LQFP64  | TRAY |

| SC32L14TR7PJR | LQFP64  | TRAY |

| SC32L14GR8PJR | LQFP64  | TRAY |

| SC32L14GR7PJR | LQFP64  | TRAY |

| SC32L14TC8PJR | LQFP48  | TRAY |

| SC32L14TC7PJR | LQFP48  | TRAY |

| SC32L14GC8PJR | LQFP48  | TRAY |

| SC32L14GC7PJR | LQFP48  | TRAY |

| SC32L14TC8QJR | QFN48   | TRAY |

| SC32L14TC7QJR | QFN48   | TRAY |

| SC32L14GC8QJR | QFN48   | TRAY |

| SC32L14GC7QJR | QFN48   | TRAY |

Note: Regarding the mass production status of specific models, please consult sales representatives from SinOne or authorized distributors for information on sample availability and lead times before starting development.

## **Content**

| 1   | Gene     | ral Descr | ription                                     |    |

|-----|----------|-----------|---------------------------------------------|----|

| 2   | Featu    | ıres      |                                             | 2  |

|     | 2.1      | Flash     |                                             | 2  |

|     | 2.2      | BootLoa   | ader                                        | 3  |

|     | 2.3      | Flash P   | rogramming and Emulation                    | 3  |

|     | 2.4      | Clock so  | ource                                       | 3  |

|     | 2.5      | Interrup  | ts (INT)                                    | 3  |

|     | 2.6      | Digital p | peripherals                                 | 3  |

|     | 2.7      | Analog    | peripherals                                 | 2  |

| Pro | duct Pe  | eripheral | Resource Table                              | 5  |

| Ord | ering lı | nformatio | on                                          | 6  |

| Con | itent    |           |                                             | 7  |

| 3   | Pin D    | escriptio | n                                           | 13 |

|     | 3.1      |           | figuration                                  |    |

|     | 3.2      | Pin Res   | source List                                 | 16 |

| 4   | Reso     | urce Diaç | gram                                        | 20 |

| 5   | Flash    |           |                                             |    |

|     | 5.1      |           | W                                           |    |

|     | 5.2      | Storage   | Block Diagram                               | 21 |

|     | 5.3      |           |                                             |    |

|     | 5.4      | APROM     | 1                                           | 22 |

|     | 5.5      |           | s User Storage Area (Genetic EEPROM)        |    |

|     | 5.6      | 4 Kbyte   | s LDROM                                     | 23 |

|     |          | 5.6.1     | BootLoader                                  | 24 |

|     | 5.7      | SRAM.     |                                             | 24 |

|     | 5.8      | Boot Are  | ea Selection (Bootstrap)                    | 24 |

|     |          | 5.8.1     | Bootstrap from APROM                        | 25 |

|     |          | 5.8.2     | Bootstrap from LDROM                        | 25 |

|     |          | 5.8.3     | Bootstrap from SRAM                         | 25 |

|     |          | 5.8.4     | Bootstrap mode configure                    | 25 |

|     | 5.9      | 96 bits l | Unique ID                                   | 25 |

|     | 5.10     | User ID   | Area                                        | 25 |

|     | 5.11     | Progran   | nming                                       | 25 |

|     |          | 5.11.1    | JTAG Specific Mode                          | 26 |

|     |          | 5.11.2    | Normal Mode (JTAG specific port is invalid) | 26 |

|     | 5.12     | Security  | / Encryption                                | 27 |

|   |        | 5.12.1            | Security Encryption Access Rights                                                                            | 27 |

|---|--------|-------------------|--------------------------------------------------------------------------------------------------------------|----|

|   | 5.13   | In Applic         | cation Programming (IAP)                                                                                     | 28 |

|   |        | 5.13.1            | IAP Operation Register Table                                                                                 | 28 |

|   |        | 5.13.2            | IAP Register Mapping                                                                                         | 31 |

|   | 5.14   | Option E          | Byte Area (Customer Option)                                                                                  | 31 |

|   |        | 5.14.1            | Customer Option Map Register                                                                                 | 32 |

| 6 | Powe   | r, Reset A        | And System Clock (RCC)                                                                                       | 35 |

|   | 6.1    | Power-c           | n Reset                                                                                                      | 35 |

|   |        | 6.1.1             | Reset Stage                                                                                                  | 35 |

|   |        | 6.1.2             | Loading Information Stage                                                                                    | 35 |

|   |        | 6.1.3             | Normal Operation Stage                                                                                       | 35 |

|   | 6.2    | Reset M           | lodes                                                                                                        | 35 |

|   |        | 6.2.1             | Hardware reset                                                                                               | 36 |

|   |        | 6.2.2             | Software reset                                                                                               | 37 |

|   |        | 6.2.3             | Boot area after the reset                                                                                    | 37 |

|   |        | 6.2.4             | Initial Reset State                                                                                          | 37 |

|   | 6.3    | Clock             |                                                                                                              | 38 |

|   |        | 6.3.1             | System Clock Source                                                                                          | 38 |

|   |        | 6.3.2             | Built-in High-Frequency 48MHz Oscillator (HIRC)                                                              | 38 |

|   |        | 6.3.3<br>High-Fre | Built-In High-Frequency Oscillator Circuit, Can Be Connected to an External 2~16MHz equency Oscillator (HXT) | 38 |

|   |        | 6.3.4             | Built-in Low-Frequency 32kHz Oscillator (LIRC)                                                               | 39 |

|   |        | 6.3.5<br>Frequer  | Built-In Low-Frequency Oscillator Circuit, Can Be Connected to an External Low-                              | 39 |

|   | 6.4    | Register          | Access Clock and Peripheral Clock Sources                                                                    | 39 |

|   |        | 6.4.1             | Register Access Clock                                                                                        | 39 |

|   |        | 6.4.2             | Peripheral Clock Source                                                                                      | 39 |

|   |        | 6.4.3             | Bus Clock                                                                                                    | 40 |

|   |        | 6.4.4             | Peripheral Clock                                                                                             | 42 |

|   |        | 6.4.5             | Peripheral Clock Block Diagram                                                                               | 42 |

|   |        | 6.4.6             | Peripheral Clock Enable Register                                                                             | 43 |

|   |        | 6.4.7             | Low Power Mode Clock                                                                                         | 43 |

| 7 | Interr | upts              |                                                                                                              | 45 |

|   | 7.1    | External          | interrupts INT0~15                                                                                           | 45 |

|   | 7.2    | Interrup          | and Events                                                                                                   | 46 |

|   | 7.3    | Interrup          | Source and Vector                                                                                            | 46 |

| 8 | Powe   | er Saving         | Mode                                                                                                         | 50 |

| 9 | Low \  | √oltage D         | etector (LPD)                                                                                                | 51 |

|   | 9.1    | Overvie           | N                                                                                                            | 51 |

|    | 9.2   | Hysteresis Function                     |    |

|----|-------|-----------------------------------------|----|

| 10 |       | )                                       |    |

|    |       | Clock Source                            |    |

|    |       | Feature                                 |    |

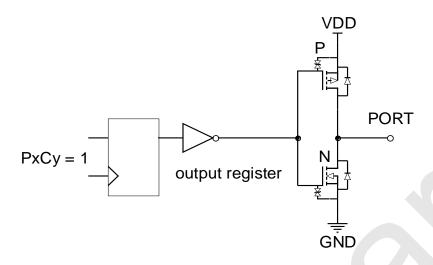

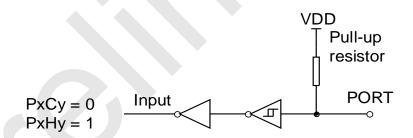

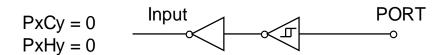

|    | 10.3  | GPIO Structure Diagram                  |    |

|    |       | 10.3.1 Strong Push-pull Output Mode     |    |

|    |       | 10.3.2 Pull-up Input Mode               |    |

| 11 | Anala | og-to-Digital Converter ADC             |    |

| '' |       | Clock source                            |    |

|    |       | Feature                                 |    |

|    |       | ADC Conversion Steps.                   |    |

|    |       | ADC Interrupt                           |    |

|    |       | ADC Structure Diagram                   |    |

| 12 |       | erature Sensor                          |    |

| 12 |       | Overview                                |    |

|    |       | Temperature Sensor Operation Steps      |    |

| 13 |       | ational Amplifier (OP)                  |    |

| .0 | -     | Overview                                |    |

|    |       | Feature                                 |    |

|    |       | OP Port Selection                       |    |

|    |       | 13.3.1 OP Accuracy Adjustment           |    |

|    |       | 13.3.2 OP Non-inverting Input Selection |    |

|    |       | 13.3.3 OP Inverting Input Selection     |    |

|    |       | 13.3.4 OP Output Selection              |    |

|    | 13.4  | OP Circuit Structure Diagram            | 58 |

| 14 |       | og Comparator CMP                       |    |

|    | 14.1  | Feature                                 | 59 |

|    | 14.2  | Analog Comparator Structure Diagram     | 59 |

| 15 | AES   | hardware accelerator (AES)              | 60 |

|    | 15.1  | Overview                                | 60 |

|    | 15.2  | Clock source                            | 60 |

|    | 15.3  | Feature                                 | 60 |

| 16 | True  | random number generator (TRNG)          | 61 |

|    | 16.1  | Overview                                | 61 |

|    | 16.2  | Clock source                            | 61 |

|    | 16.3  | Feature                                 | 61 |

| 17 | UAR   | Г0~5                                    | 62 |

|    | 17.1  | Clock Source                            | 62 |

|    | 17.2  | Feature                                     | 62 |

|----|-------|---------------------------------------------|----|

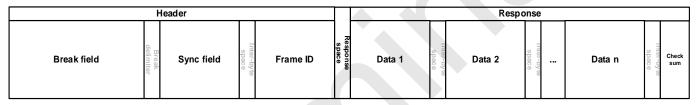

|    | 17.3  | UART2-LIN                                   | 63 |

|    |       | 17.3.1 LIN Frame Structure                  | 63 |

|    |       | 17.3.2 LIN Master Mode                      | 63 |

|    |       | 17.3.3 LIN Slave Mode                       | 63 |

| 18 | Smar  | t Card Interface (SMCI)                     | 65 |

|    | 18.1  | Overview                                    | 65 |

|    | 18.2  | Clock Source                                | 65 |

|    | 18.3  | Feature                                     | 65 |

|    | 18.4  | Operating Modes                             | 65 |

|    |       | 18.4.1 Smart Card Description               | 65 |

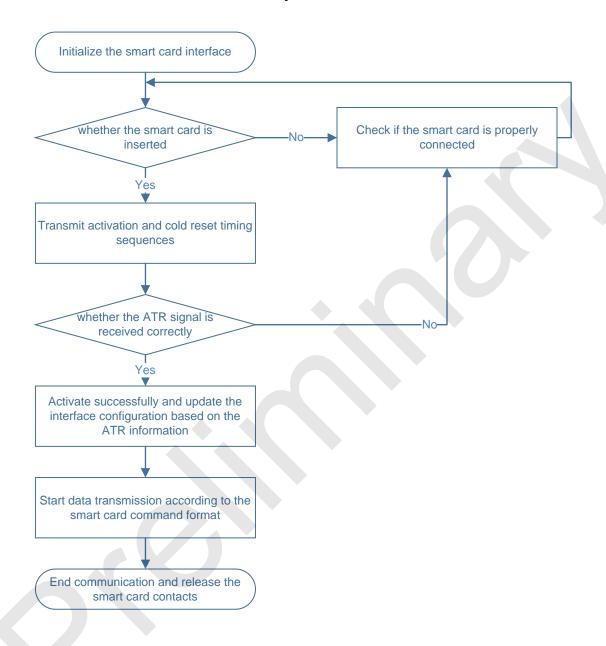

|    | 18.5  | Basic Smart Card Interface Operation Flow   | 66 |

| 19 | SPI0/ | /1                                          | 67 |

|    | 19.1  | Clock Source                                | 67 |

|    | 19.2  | SPI0/1 Feature                              | 67 |

| 20 | TWI0  | /1                                          | 68 |

|    | 20.1  | Clock Source                                | 68 |

|    | 20.2  | TWI0/1 Feature                              | 68 |

|    |       | TWI Signal Description                      |    |

| 21 |       | ware Watchdog WDT                           |    |

|    |       | Overview                                    |    |

|    |       | Clock Source                                |    |

| 22 | втм   |                                             | 70 |

|    |       | Overview                                    |    |

|    |       | Clock Source                                |    |

|    |       | Feature                                     |    |

| 23 |       | in CRC Module                               |    |

|    |       | Overview                                    |    |

|    |       | Clock Source                                |    |

|    |       | Feature                                     |    |

| 24 |       | 0: 8 Channels of 16-bit Multifunctional PWM |    |

|    |       | Overview                                    |    |

|    |       | Clock Source                                |    |

|    |       | Feature                                     |    |

|    |       | PWM0 Structure Diagram                      |    |

|    |       | PWM0 General Configuration                  |    |

|    | -     | 24.5.1 Output Mode                          |    |

|    |       | 24.5.2 Alignment Type                       |    |

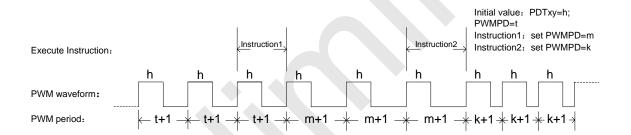

|    |       | 24.5.3 Duty Cycle Change Characteristics    |    |

|    |       | ,                                           |    |

|    |       | 24.5.4     | Period Change Characteristics              | 74 |

|----|-------|------------|--------------------------------------------|----|

|    |       | 24.5.5     | Relationship Between Period and Duty Cycle | 74 |

| 25 | 32-CI | nannel Hi  | gh-Sensitivity Touch Circuit (TK)          | 76 |

| 26 | Real- | Time Clo   | ck (RTC)                                   | 77 |

|    | 26.1  | Overviev   | N                                          | 77 |

|    | 26.2  | Clock So   | ource                                      | 77 |

|    | 26.3  | Feature    |                                            | 77 |

|    | 26.4  | Block Di   | agram                                      | 77 |

| 27 | Low-l | Power Co   | unter (LPC)                                | 78 |

|    | 27.1  | Overviev   | N                                          | 78 |

|    | 27.2  | Feature    |                                            | 78 |

|    | 27.3  | LPC Blo    | ck Diagram                                 | 78 |

| 28 | 16-bi | t Timers ( | Timer0~Timer7)                             | 79 |

|    | 28.1  | Clock So   | ource                                      | 79 |

|    | 28.2  | Feature    |                                            | 79 |

|    | 28.3  | Counting   | g method                                   | 79 |

|    |       | 28.3.1     | Counting Method in Timer Mode              | 79 |

|    |       | 28.3.2     | Counting Method in PWM Mode                | 79 |

|    | 28.4  | Timer Si   | gnal Port                                  | 79 |

|    | 28.5  | Interrupt  | s and Corresponding Flags for TIM          | 80 |

|    | 28.6  | Timer O    | perating Mode                              | 80 |

| 29 | LCD   | Driver     |                                            | 81 |

|    | 29.1  | Clock So   | ource                                      | 81 |

|    | 29.2  | Built-in 8 | 3 COM x 51 SEG LCD Driver                  | 81 |

|    |       | 29.2.1     | Resistor LCD driver                        | 81 |

|    |       | 29.2.2     | Capacitor LCD driver                       | 81 |

| 30 | Direc | t Memory   | Access (DMA)                               | 83 |

|    | 30.1  | Overviev   | <i>N</i>                                   | 83 |

|    | 30.2  | Clock So   | ource                                      | 83 |

|    | 30.3  | Feature    |                                            | 83 |

|    | 30.4  | Function   | n Description                              | 83 |

|    |       | 30.4.1     | Transmission                               | 83 |

|    |       | 30.4.2     | DMA Access Restriction                     | 84 |

|    |       | 30.4.3     | Channel Priority                           | 84 |

|    |       | 30.4.4     | Single Transmission and Burst Transmission | 84 |

|    |       | 30.4.5     | Loop Mode                                  | 84 |

| 31 | SysTi | ick        | · · · · · · · · · · · · · · · · · · ·      | 85 |

|    | •     |            | ource                                      |    |

|    | 31.2  | SysTick    | Calibration Register Default Value         | 85 |

### SC32L14T/14G series

| 32 | Elect | rical Char | racteristics                                                                                 | 86  |

|----|-------|------------|----------------------------------------------------------------------------------------------|-----|

|    | 32.1  | Recomn     | nended Operating Conditions                                                                  | 86  |

|    | 32.2  | Absolute   | e Maximum Ratings                                                                            | 86  |

|    | 32.3  | Flash R    | OM Parameters                                                                                | 86  |

|    | 32.4  | Power C    | Consumption                                                                                  | 87  |

|    |       | 32.4.1     | $V_{DD}$ = 5V, $T_A$ = +25 $^{\circ}\mathrm{C}$ , boot from APROM unless otherwise specified | 87  |

|    |       | 32.4.2     | $V_{DD}$ = 3.3V, $T_A$ = +25°C, boot from APROM unless otherwise specified                   | 88  |

|    | 32.5  |            | arameter                                                                                     |     |

|    |       | 32.5.1     | V <sub>DD</sub> = 5V, T <sub>A</sub> = +25°C, unless otherwise specified                     | 89  |

|    |       | 32.5.2     | V <sub>DD</sub> = 3.3V, T <sub>A</sub> = +25℃, unless otherwise specified                    | 89  |

|    | 32.6  | AC Elec    | etrical Characteristics                                                                      | 90  |

|    | 32.7  | TK Chai    | racteristics                                                                                 | 90  |

|    | 32.8  | BTM Ch     | naracteristics                                                                               | 90  |

|    | 32.9  | WDT Ch     | naracteristics                                                                               | 91  |

|    | 32.10 | ADC Ch     | naracteristics                                                                               | 91  |

|    | 32.11 | CMP Ele    | ectrical Characteristics                                                                     | 92  |

|    | 32.12 | OP Elec    | ctrical Characteristic                                                                       | 92  |

|    |       |            | ectrical Characteristics                                                                     |     |

| 33 |       |            | mation                                                                                       |     |

| 34 | Revis | sion Histo | ry                                                                                           | 100 |

| 35 | Impo  | rtant Noti | ce                                                                                           | 101 |

# 3 Pin Description

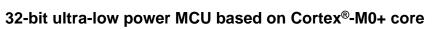

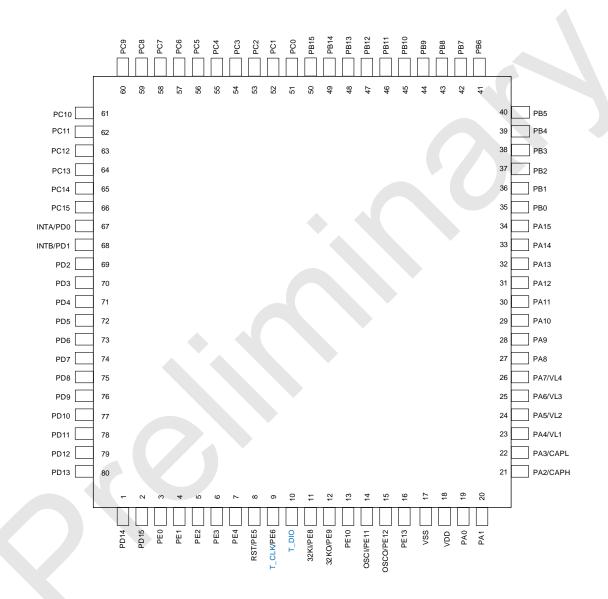

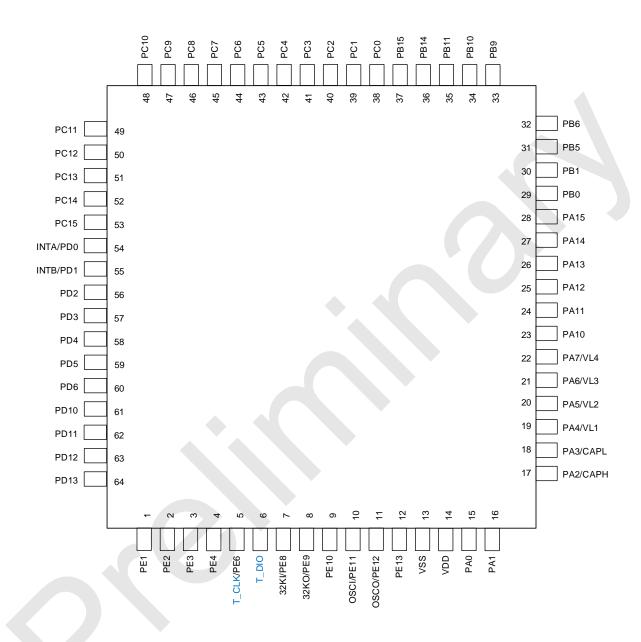

## 3.1 Pin Configuration

Note: TK function is only supported on the SCL14T series.

80PIN Pin Diagram Suitable for LQFP80 package

64PIN Pin Diagram Suitable for LQFP64 package

48PIN Pin Diagram Suitable for LQFP48, QFN48 package

### 3.2 Pin Resource List

| LQFP48/<br>QFN48 | LQFP64 | LQFP80 | GPIO | 特殊    | UART   | TWI     | SPI      | LCD   | TK   | ADC   | PWM-8  | PWM      | TxEX/Tx    | CMP  | OP    | INT   |

|------------------|--------|--------|------|-------|--------|---------|----------|-------|------|-------|--------|----------|------------|------|-------|-------|

| -                | -      | 1      | PD14 |       | (TxD2) |         | (MISO0A) | SEG30 | TK0  | AIN19 |        | T7PWM1   | T7EX       |      |       | INT14 |

| -                | -      | 2      | PD15 |       | (RxD2) | (SDA0A) | (MOSI0A) | SEG29 | TK1  | AIN18 |        |          |            |      |       | INT15 |

| -                | -      | 3      | PE0  |       |        | (SCL0A) | (SCK0A)  | SEG28 | TK2  |       |        |          |            | CMPR |       | INT0  |

| -                | 1      | 4      | PE1  |       |        |         |          |       | ткз  |       |        |          |            | CMP3 | OP_N  | INT1  |

| -                | 2      | 5      | PE2  |       |        | (SCL1A) | (SCK1A)  |       | TK4  |       |        |          |            | CMP2 | OP_P0 | INT2  |

| -                | 3      | 6      | PE3  |       | (RxD1) | (SDA1A) | (MOSI1A) |       | TK5  |       |        |          |            | CMP1 | OP_P1 | INT3  |

| -                | 4      | 7      | PE4  |       | (TxD1) |         | (MISO1A) |       | TK6  |       |        | T5PWM0   | T5CAP/T5   | CMP0 | OP_0  | INT4  |

| -                | -      | 8      | PE5  | RST   |        |         |          |       |      |       |        | (T7PWM0) | (T7CAP/T7) |      |       | INT5  |

| 3                | 5      | 9      | PE6  | T_CLK | RxD3   |         |          |       |      |       |        | (T0PWM0) | (T0CAP/T0) |      |       | INT6  |

| 4                | 6      | 10     | -    | T_DIO | TxD3   |         |          |       |      |       |        |          |            |      |       | -     |

| 5                | 7      | 11     | PE8  | 32KI  |        |         |          |       |      |       | PWM0_3 |          |            |      |       | INT8  |

| 6                | 8      | 12     | PE9  | 32KO  |        |         |          |       |      |       | PWM0_2 |          |            |      |       | INT9  |

| 7                | 9      | 13     | PE10 |       |        |         |          |       |      |       | PWM0_1 |          |            |      |       | INT10 |

| 8                | 10     | 14     | PE11 | OSCI  |        |         |          |       |      |       | PWM0_0 |          |            |      |       | INT11 |

| 9                | 11     | 15     | PE12 | osco  |        |         |          |       |      |       |        |          |            |      |       | INT12 |

| 10               | 12     | 16     | PE13 |       |        |         | (MISO0B) |       | CMOD |       |        |          |            |      |       | INT13 |

| 11               | 13     | 17     | VSS  | VSS   |        |         |          |       |      |       |        |          |            |      |       |       |

| 12               | 14     | 18     | VDD  | VDD   |        |         |          |       |      |       |        |          |            |      |       |       |

| 13               | 15     | 19     | PA0  |       |        | (SDA0B) | (MOSI0B) | SEG27 |      |       |        | (T2PWM0) | (T2CAP/T2) |      |       | INT0  |

| 14               | 16     | 20     | PA1  |       |        | (SCL0B) | (SCK0B)  | SEG26 |      |       |        | (T1PWM0) | (T1CAP/T1) |      |       | INT1  |

| 15               | 17     | 21     | PA2  | CAPH  |        |         |          |       |      |       |        | (T3PWM0) | (T3CAP/T3) |      |       | INT2  |

| 16               | 18     | 22     | PA3  | CAPL  |        |         |          |       |      |       |        | (T4PWM0) | (T4CAP/T4) |      |       | INT3  |

| LQFP48/<br>QFN48 | LQFP64 | LQFP80 | GPIO | 特殊  | UART              | TWI     | SPI      | LCD   | тк   | ADC         | PWM-8  | PWM      | TxEX/Tx    | CMP | OP | INT   |

|------------------|--------|--------|------|-----|-------------------|---------|----------|-------|------|-------------|--------|----------|------------|-----|----|-------|

| 17               | 19     | 23     | PA4  | VL1 |                   |         |          |       |      |             | PWM0_4 |          |            |     |    | INT4  |

| 18               | 20     | 24     | PA5  | VL2 |                   |         |          |       |      |             | PWM0_5 |          |            |     |    | INT5  |

| 19               | 21     | 25     | PA6  | VL3 |                   |         |          |       |      |             | PWM0_6 |          |            |     |    | INT6  |

| 20               | 22     | 26     | PA7  | VL4 |                   |         |          |       |      |             | PWM0_7 | (T6PWM0) | (T6CAP/T6) |     |    | INT7  |

| -                |        | 27     | PA8  |     | TxD1              |         |          | SEG25 |      |             |        |          |            |     |    | INT8  |

| -                | -      | 28     | PA9  |     | RxD1              |         |          | SEG24 |      |             |        |          |            |     |    | INT9  |

| -                | 23     | 29     | PA10 |     |                   | (SCL1B) | (SCK1B)  | SEG23 |      |             |        |          |            |     |    | INT10 |

| 21               | 24     | 30     | PA11 |     |                   | (SDA1B) | (MOSI1B) | SEG22 | TK7  |             |        | T1PWM0   | T1CAP/T1   |     |    | INT11 |

| 22               | 25     | 31     | PA12 |     |                   |         | (MISO1B) | SEG21 | TK8  |             |        |          |            |     |    | INT12 |

| 23               | 26     | 32     | PA13 |     |                   |         |          | SEG20 | TK9  | <b>&gt;</b> |        | T3PWM0   | T3CAP/T3   |     |    | INT13 |

| 24               | 27     | 33     | PA14 |     | (RxD0)            |         |          | SEG19 | TK10 |             |        |          |            |     |    | INT14 |

| -                | 28     | 34     | PA15 |     | (TxD0)            |         |          | SEG18 | TK11 |             |        |          |            |     |    | INT15 |

| -                | 29     | 35     | PB0  |     |                   |         |          | SEG17 | TK12 |             |        |          |            |     |    | INT0  |

| -                | 30     | 36     | PB1  |     |                   |         |          | SEG16 | TK13 |             |        |          |            |     |    | INT1  |

| -                | -      | 37     | PB2  |     |                   |         |          | SEG15 |      |             |        |          |            |     |    | INT2  |

| -                | -      | 38     | PB3  |     | RxD4              |         |          | SEG14 |      |             |        |          |            |     |    | INT3  |

| -                | -      | 39     | PB4  |     | TxD4              |         |          | SEG13 |      |             |        |          |            |     |    | INT4  |

| -                | 31     | 40     | PB5  |     |                   |         |          | SEG12 |      |             | FLT    |          |            |     |    | INT5  |

| -                | 32     | 41     | PB6  |     |                   |         |          | SEG11 |      |             |        | T6PWM1   | T6EX       |     |    | INT6  |

| -                | -      | 42     | РВ7  |     | (RxD5/SCCL<br>K0) |         |          | SEG10 |      |             |        | T6PWM0   | T6CAP/T6   |     |    | INT7  |

| -                |        | 43     | PB8  |     | (TxD5/SCIO<br>0)  |         |          | SEG9  |      |             |        | T2PWM1   | T2EX       |     |    | INT8  |

| -                | 33     | 44     | PB9  |     | RxD5/SCCL<br>K0   |         |          | SEG8  |      |             |        | T2PWM0   | T2CAP/T2   |     |    | INT9  |

| LQFP48/<br>QFN48 | LQFP64 | LQFP80 | GPIO | 特殊   | UART       | TWI     | SPI      | LCD       | тк       | ADC   | PWM-8 | PWM      | TxEX/Tx    | СМР | ОР | INT   |

|------------------|--------|--------|------|------|------------|---------|----------|-----------|----------|-------|-------|----------|------------|-----|----|-------|

| 25               | 34     | 45     | PB10 |      | TxD5/SCIO0 |         |          | SEG7      |          |       |       | T0PWM1   | T0EX       |     |    | INT10 |

| 26               | 35     | 46     | PB11 |      |            |         | (MISO1C) | SEG6      |          |       |       | T0PWM0   | T0CAP/T0   |     |    | INT11 |

| 27               | -      | 47     | PB12 |      |            | (SDA1C) | (MOSI1C) | SEG5      |          |       |       |          |            |     |    | INT12 |

| 28               |        | 48     | PB13 |      |            | (SCL1C) | (SCK1C)  | SEG4      |          |       |       |          |            |     |    | INT13 |

| 29               | 36     | 49     | PB14 |      |            |         |          | COM7/SEG3 |          |       |       |          |            |     |    | INT14 |

| 30               | 37     | 50     | PB15 |      |            |         |          | COM6/SEG2 |          |       |       |          |            |     |    | INT15 |

| 31               | 38     | 51     | PC0  |      |            |         |          | COM5/SEG1 |          |       |       |          |            |     |    | INT0  |

| 32               | 39     | 52     | PC1  |      |            |         |          | COM4/SEG0 |          |       |       |          |            |     |    | INT1  |

| 33               | 40     | 53     | PC2  |      |            |         |          | СОМЗ      |          |       |       |          |            |     |    | INT2  |

| 34               | 41     | 54     | PC3  |      |            |         |          | COM2      |          |       |       |          |            |     |    | INT3  |

| 35               | 42     | 55     | PC4  |      |            |         |          | COM1      |          |       |       |          |            |     |    | INT4  |

| 36               | 43     | 56     | PC5  |      |            |         |          | СОМО      | <b>*</b> |       |       |          |            |     |    | INT5  |

| -                | 44     | 57     | PC6  |      | (TxD3)     |         | MISO0    | SEG54     |          |       |       | T1PWM1   | T1EX       |     |    | INT6  |

| -                | 45     | 58     | PC7  |      | (RxD3)     | SDA0    | MOSI0    | SEG53     |          |       |       |          |            |     |    | INT7  |

| -                | 46     | 59     | PC8  |      |            | SCL0    | SCK0     | SEG52     |          |       |       |          |            |     |    | INT8  |

| -                | 47     | 60     | PC9  |      | TxD0       |         |          | SEG51     |          |       |       |          |            |     |    | INT9  |

| -                | 48     | 61     | PC10 |      | RxD0       |         |          | SEG50     |          |       |       |          |            |     |    | INT10 |

| -                | 49     | 62     | PC11 |      |            |         |          | SEG49     |          |       |       | T5PWM1   | T5EX       |     |    | INT11 |

| -                | 50     | 63     | PC12 |      |            |         |          | SEG48     | TK14     | AIN17 |       | (T5PWM0) | (T5CAP/T5) |     |    | INT12 |

| -                | 51     | 64     | PC13 |      | TxD2       |         | MISO1    | SEG47     | TK15     | AIN16 |       |          |            |     |    | INT13 |

| -                | 52     | 65     | PC14 |      | RxD2       | SDA1    | MOSI1    | SEG46     | TK16     | AIN15 |       |          |            |     |    | INT14 |

| -                | 53     | 66     | PC15 |      |            | SCL1    | SCK1     | SEG45     | TK17     | AIN14 |       |          |            |     |    | INT15 |

| 37               | 54     | 67     | PD0  | INTA |            |         |          | SEG44     | TK18     | AIN13 |       | T7PWM0   | T7CAP/T7   |     |    | INT0  |

| 38               | 55     | 68     | PD1  | INTB |            |         |          | SEG43     | TK19     | AIN12 |       | T4PWM0   | T4CAP/T4   |     |    | INT1  |

| 39               | 56     | 69     | PD2  |      |            |         |          | SEG42     | TK20     | AIN11 |       |          |            |     |    | INT2  |

| LQFP48/<br>QFN48 | LQFP64 | LQFP80 | GPIO | 特殊 | UART   | TWI     | SPI      | LCD   | тк   | ADC   | PWM-8 | PWM    | TxEX/Tx | СМР | OP | INT   |

|------------------|--------|--------|------|----|--------|---------|----------|-------|------|-------|-------|--------|---------|-----|----|-------|

| 40               | 57     | 70     | PD3  |    |        |         |          | SEG41 | TK21 | AIN10 |       |        |         |     |    | INT3  |

| 41               | 58     | 71     | PD4  |    |        |         |          | SEG40 | TK22 | AIN9  |       |        |         |     |    | INT4  |

| 42               | 59     | 72     | PD5  |    |        |         |          | SEG39 | TK23 | AIN8  |       |        |         |     |    | INT5  |

| 43               | 60     | 73     | PD6  |    |        |         |          | SEG38 | TK24 | AIN7  |       |        |         |     |    | INT6  |

| 44               | -      | 74     | PD7  |    | (TxD4) |         | (MISOOC) | SEG37 | TK25 | AIN6  |       |        |         |     |    | INT7  |

| 45               |        | 75     | PD8  |    | (RxD4) | (SDA0C) | (MOSIOC) | SEG36 | TK26 | AIN5  |       |        |         |     |    | INT8  |

| 46               | -      | 76     | PD9  |    |        | (SCL0C) | (SCK0C)  | SEG35 | TK27 | AIN4  |       |        |         |     |    | INT9  |

| 47               | 61     | 77     | PD10 |    |        |         |          | SEG34 | TK28 | AIN3  |       | T4PWM1 | T4EX    |     |    | INT10 |

| 48               | 62     | 78     | PD11 |    |        |         |          | SEG33 | TK29 | AIN2  |       | T3PWM1 | T3EX    |     |    | INT11 |

| 1                | 63     | 79     | PD12 |    |        |         |          | SEG32 | TK30 | AIN1  |       |        |         |     |    | INT12 |

| 2                | 64     | 80     | PD13 |    |        |         |          | SEG31 | TK31 | AIN0  |       |        |         |     |    | INT13 |

# 4 Resource Diagram

### 5 Flash

### 5.1 Overview

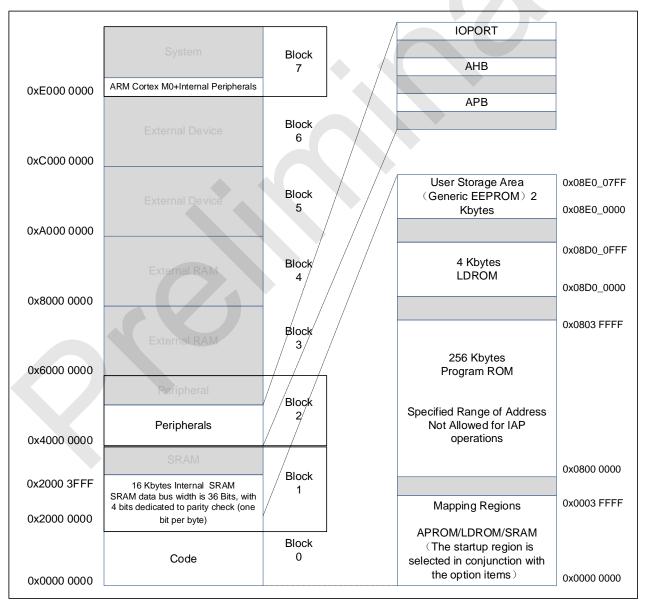

The program memory, data memory, and registers are arranged within a single linear (i.e., contiguous) 4 GB address space. Each byte is encoded in the storage in little-endian format, meaning that the least significant byte of a word is the lowest numbered byte, while the most significant byte is the highest numbered byte. The addressable storage space is divided into 8 main blocks, each block being 512 MB in size.

### 5.2 Storage Block Diagram

SC32L14T/14G Series Memory Mapping Diagram

### 5.3 Feature

- The Flash width is 32 bits, and it can be rewritten up to 100,000 times

- Data retention time is over 100 years at room temperature

- The structure of the Flash includes:

- Maximum 256 Kbytes APROM

- 4 Kbytes LDROM

- 2 Kbytes user storage area (generic EEPROM)

- 16 Kbytes Internal SRAM, support parity check

- 96 bits Unique ID

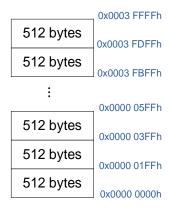

### 5.4 APROM

- APROM of SC32L14xx8 series has 256K bytes

- APROM of SC32L14xx7 series has 128K bytes

- Sector Size: 512 bytes

- Supports: Read/Write/Sector Erase/Chip Erase/Blank Check

- The CPU (Cortex®-M0+) accesses Flash through the AHB bus

- The program defaults to booting from APROM, and users can select programs to boot from other areas such as SRAM/LDROM using the customer option OP BL[1:0]

- Read Protection: After enabling read protection, only a program that runs from APROM can read information from APROM. Other areas or third-party tools cannot access information from APROM

- Write Protection: Provides two hardware write protection regions where IAP operations are prohibited.

Users can set the range of the two write protection regions in units of sectors based on actual needs

The 256 Kbytes of APROM is divided into 512 sectors, with each sector being 512 bytes. During programming, the sector to which the target address belongs will be forcibly erased by the programmer before writing data. During user write operations, the sector must be erased first before writing data.

SC32L14T 256 Kbytes Flash ROM Sector Partition Illustration

The 128 Kbytes of APROM is divided into 256 sectors, with each sector being 512 bytes. During programming, the sector to which the target address belongs will be forcibly erased by the programmer

before writing data. During user write operations, the sector must be erased first before writing data.

|           | 0x0001 FFFFh |

|-----------|--------------|

| 512 bytes | 0x0001 FDFFh |

| 512 bytes | 0x0001 FBFFh |

| :         | 0x0000 05FFh |

| 512 bytes | 0x0000 03FFh |

| 512 bytes | 0x0000 01FFh |

| 512 bytes | 0x0000 0000h |

SC32L14xx7 series 128 Kbytes APROM Sector Partition Illustration

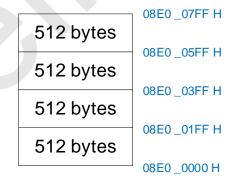

### 5.5 2 Kbytes User Storage Area (Genetic EEPROM)

The 2K bytes of independent EEPROM area is addressed from 0x08E0\_0000 H to 0x08E0\_07FF H, as set by the IAPADE register. This independent EEPROM can be written to repeatedly up to 100,000 times, and it is designed to retain data for over 100 years at room temperature. The independent EEPROM supports various operations including blank check, programming, verification, erasure, and reading functions.

EEPROM has 4 sectors, with each sector being 512 bytes.

SC32L14T EEPROM Sector Partition Illustration

Note: The EEPROM has a write cycle endurance of 100,000 times. Users should avoid exceeding the rated write cycles of the EEPROM to prevent any anomalies!

## 5.6 4 Kbytes LDROM

4 Kbytes of system storage area, factory-programmed with BootLoader program, Users cannot modify or access this area

Embedded Bootloader Program: The fixed ISP program is publicly available, allowing reprogramming

of Flash via UART. The program waits for upgrade commands, and if no update command is received

within 500 milliseconds, it jumps to APROM for execution (0X0800 0000)

### 5.6.1 BootLoader

Supports two Bootloader modes:

- Software Approach: Directly partition BootLoader and APP areas in software. Easy sharing interrupts

of BootLoader and APP by modifying VTOR. Flexible adjustment of the size of each area

- Hardware Approach: 4 Kbytes fixed "LDROM" as a dedicated BootLoader area that users cannot read

or write

- LDROM serves as a fixed BootLoader space with factory-programmed program, and users cannot read or write

- Embedded Bootloader Program: The embedded bootloader program resides in LDROM and is programmed during the production stage. The fixed ISP program is publicly available, allowing reprogramming of Flash via UART

### 5.7 SRAM

- Internal SRAM: 16 Kbytes, address 0x2000 0000 ~ 0x2000 3FFF

- Supports parity check

- An additional 2Kbytes RAM is used for parity checking, which means SRAM data bus width is 36 bits, with 4 bits dedicated to parity check (one bit per byte)

- The parity check bits are calculated and saved when writing to the SRAM, and automatically verified upon reading. If a bit fails, an unmaskable interrupt (Cortex®-M0+ NMI) will be generated

- Provides an independent SRAM parity error flag, SRAMPEIF

Note: When SRAM parity check is enabled, it is recommended to perform a software initialization of the entire SRAM at the beginning of the code to prevent parity check errors when reading from uninitialized locations.

- Users can choose to start the program from SRAM by configuring the customer option OP\_BL[1:0]

- It supports byte, half-word (16-bit), or word (32-bit) access at the maximum system clock frequency, with no waiting states. Therefore, it can be accessed by both the CPU and DMA

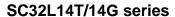

## 5.8 Boot Area Selection (Bootstrap)

After a reset, users can independently configure the desired bootstrap mode.

After exiting the standby mode, the startup mode configuration can be resampled. Once this startup delay has ended, the CPU will fetch the stack top value from address 0x00000000 and then begin executing code from the bootstrap memory starting at 0x00000004.

There are three options for bootstrap area selection: Main Flash Memory Area, System Flash Memory Area and SRAM, described in detail as follows:

### 5.8.1 Bootstrap from APROM

APROM is aliased in the bootstrap memory space (0x00000000) but can also be accessed from its original memory space (0x08000000). In other words, the program can start accessing from either address 0x00000000 or 0x08000000.

### 5.8.2 Bootstrap from LDROM

- 4 Kbytes LDROM serves as a fixed BootLoader space with factory-programmed program, Users cannot modify or access this area

- Embedded Bootloader Program: The embedded bootloader program resides in LDROM and is programmed during the production stage. The fixed ISP program is publicly available, allowing reprogramming of Flash via UART

### 5.8.3 Bootstrap from SRAM

SRAM has an alias in the bootstrap memory space (0x0000 0000) but can also be accessed from its original memory space (0x2000 0000).

### 5.8.4 Bootstrap mode configure

The bootstrap modes can be controlled by the register bits BTLD[1:0] in conjunction with the software reset (RST) control bit, both protected by the IAP\_KEY::

- ① Set BTLD[1:0]=0x00: the chip boots from APROM after a software reset.

- ② Set BTLD[1:0]=0x01: the chip boots from LDROM after a software reset.

- 3 Set BTLD[1:0]=0x10: the chip boots from SRAM after a software reset.

The initial boot region selection during power-up can be configured by customer option bits OP\_BL[1:0]:

- (1) Set OP\_BL[1:0]=0x00 in customer option: the chip boots from APROM after a software reset.

- ② Set OP\_BL[1:0]=0x01 in customer option: the chip boots from LDROM after a software reset.

- 3 Set OP\_BL[1:0]=0x10 in customer option: the chip boots from SRAM after a software reset.

### 5.9 96 bits Unique ID

The SC32L14T provides an independent Unique ID area. A 96-bit unique code can be pre-programmed before leaving the factory to ensure the uniqueness of the chip. The only way for the user to obtain the serial number is to read through the IAP instruction.

### 5.10 User ID Area

User ID area, where user-customized ID is pre-programmed when leaving the factory. Users can read the User ID area, but cannot write the User ID area.

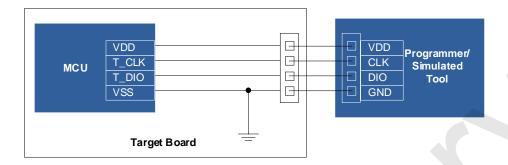

### 5.11 Programming

The SC32L14T/14G's Flash can be programmed through T\_DIO, T\_CLK, VDD, VSS, the specific connection

relationship is as follows:

ICP mode Flash Writer programming connection diagram

T\_DIO、T\_CLK is a 2-wire JTAG programming and emulation signal line. Users can configure the mode of these two ports through the Customer Option when programming.

Note: Ports of UART3 support two mapping schemes:

Mapping 1: RXD3 / TXD3Mapping 2: RXD3A / TXD3A

When Mapping 1 (RXD3/TXD3) is selected, these pins are multiplexed with the system's programming/debug interface (T\_CLK/T\_DIO). Under this mapping, if full-duplex communication is enabled, T\_CLK / T\_DIO might conflict with the receive timing of UART3's RXD3, leading to communication abnormalities. Therefore, when selecting Mapping 1, UART3 must be configured for half-duplex communication mode to avoid this hardware conflict and ensure communication stability.

If full-duplex UART communication is required, please map the pins to Mapping 2 (RXD3A/TXD3A).

### 5.11.1 JTAG Specific Mode

T\_DIO,T\_CLK are specific port for programming and emulation, and other functions multiplexed with it are not available. This mode is generally used in the online debugging stage, which is convenient for users to simulate and debug. After the JTAG special mode takes effect, the chip can directly enter the programming or emulation mode without powering on and off again.

#### 5.11.2 Normal Mode (JTAG specific port is invalid)

The JTAG function is not available, and other functions multiplexed with it can be used normally. This mode can prevent the programming port from occupying the MCU pins, which is convenient for users to maximize the use of MCU resources.

Note: When the invalid configuration setting of the JTAG dedicated port is successful, the chip must be completely powered off and then on again to enter the programming or emulation mode, which will affect the programming and emulation in the live mode. SinOne recommends that users select the invalid configuration

of the JTAG dedicated port during mass production and programming, and select the JTAG mode during the development and debugging phase.

Related Customer Option is as followed:

| Register       | R/W | Description                        | Reset Value |

|----------------|-----|------------------------------------|-------------|

| COPT1_CFG@0xC2 | R/W | Customer Option Mapping Register 1 | 0x0000_0000 |

| 7     | 6      | 5      | 4 | 3 | 2 | 1    | 0       |

|-------|--------|--------|---|---|---|------|---------|

| ENWDT | DISJTG | DISRST | - | - | - | OP_B | BL[1:0] |

| Bit number | Bit Mnemonic | Description                                                      |

|------------|--------------|------------------------------------------------------------------|

|            |              | JTAG Ports Switch Control Bit                                    |

| 6          | DISJTG       | 0: JTAG mode enabled, the corresponding pins can only be used as |

| 6 D        | DISTIG       | T_CLK and T_DIO                                                  |

|            |              | 1: Normal mode, JTAG function disabled                           |

#### 5.12 **Security Encryption**

- The SC32L14T/14G series mainly involves encrypting the APROM for read protection. Users can configure the read protection encryption feature during programming through the customer option in the dedicated programming host; enable flash read protection can enter encryption mode: The chip defaults to a non-encrypted state while leaving the factory

- The read protection encryption feature has no mapped registers. Users can only modify it after config the customer option in the dedicated programming host and programming

- Encryption Disabled: Operations such as reading, programming, and erasing can be performed on APROM. These operations can be also performed on Bytes and backup registers

- **Encryption Enabled:**

- Enable from APROM: Code executed in user mode (booting from user APROM) can perform all operations on APROM

- Debug, enable from SRAM and LDROM: In debug mode or when code is booted from SRAM or LDROM, APROM is completely inaccessible

- Disabling encryption requires a full erase operation on APROM

### 5.12.1 Security Encryption Access Rights

|                         |      | Encryp | tion Disabl    | ed Status     |                                  |           | Read Prote | tection Encryption Status |               |                                  |  |

|-------------------------|------|--------|----------------|---------------|----------------------------------|-----------|------------|---------------------------|---------------|----------------------------------|--|

| Boot Area/Tools         | Read | Write  | Block<br>Erase | Full<br>Erase | Operate Write- Protection Region | Read      | Write      | Block<br>Erase            | Full<br>Erase | Operate Write- Protection Region |  |

| Bootstrap from<br>APROM | V    | V      | V              | \             | Forbid                           | $\sqrt{}$ | V          | V                         | \             | Forbid                           |  |

|                              | Encryption Disabled Status |          |                |               |                                  | Read Protection Encryption Status |        |                |               |                                  |

|------------------------------|----------------------------|----------|----------------|---------------|----------------------------------|-----------------------------------|--------|----------------|---------------|----------------------------------|

| Boot Area/Tools              | Read                       | Write    | Block<br>Erase | Full<br>Erase | Operate Write- Protection Region | Read                              | Write  | Block<br>Erase | Full<br>Erase | Operate Write- Protection Region |

| Debug/Bootstrap<br>from SRAM | V                          | V        | V              | V             | Forbid                           | Forbid                            | Forbid | Forbid         | Forbid        | Forbid                           |

| Bootstrap from LDROM         | V                          | <b>V</b> | <b>V</b>       | <b>V</b>      | <b>V</b>                         | Forbid                            | Forbid | Forbid         | 1             | Forbid                           |

### 5.13 In Application Programming (IAP)

The IAP (In Application Programming) area in the APROM of SC32L14T/14G allows users to perform remote program updates through IAP operations. Users can also retrieve information from the Unique ID or User ID areas by IAP read operations. Before performing IAP write operations, users must carry out sector erasure for the target address sector.

The chip allows global IAP operations in the APROM by default while leaving the factory. Internally, the chip provides two sets of flash write protection regions. These regions are set based on sector units, and the protected areas are restricted from IAP operations. The rules for setting these regions are as follows:

| IAPPORx Register Value (x=A or B) | IAPPOR Protection Area                |

|-----------------------------------|---------------------------------------|

| IAPPORx_ST = IAPPORx_ED           | Sector IAPPORx                        |

| IAPPORx_ST > IAPPORx_ED           | No protection                         |

| IAPPORx_ST < IAPPORx_ED           | Sectors from IAPPORx_ST to IAPPORx_ED |

User can configure the two APROM write-protected areas via "Flash sectors protection" in the Customer Option item while programming.